发布日期:2024-12-18 12:27 点击次数:73

作家 | ZeR0

剪辑 | 漠影

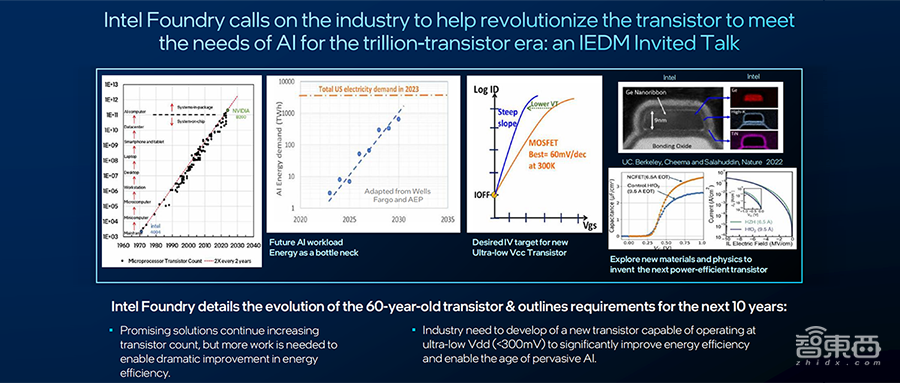

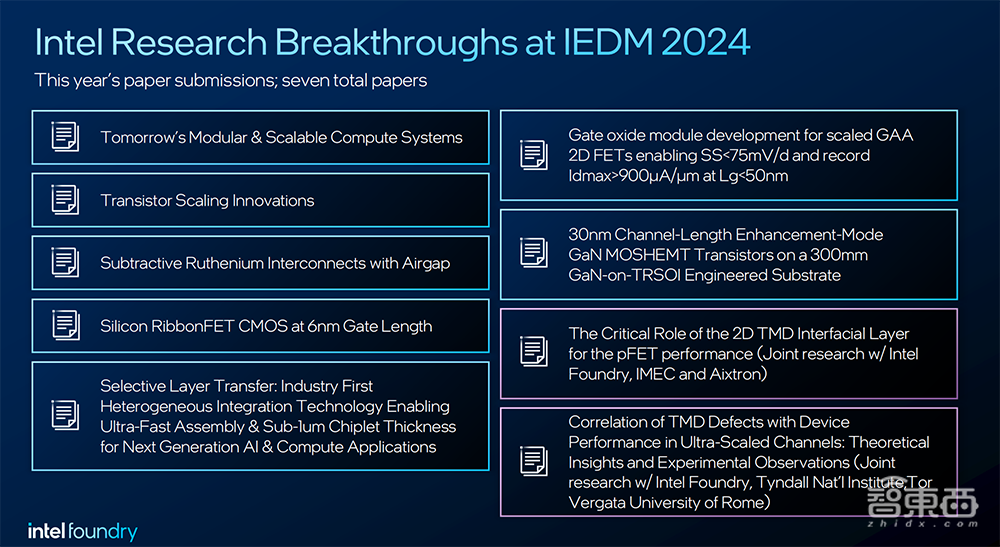

芯东西12月16日报谈,在IEDM 2024(2024年IEEE海外电子器件会议)上,英特尔代工展示了包括先进封装、晶体管微缩、互连缩放等在内的多项时期毁坏,以助力推动半导体行业不才一个十年及更永恒的发展。

英特尔通过改造封装时期将芯片封装中的朦拢量进步高达100倍,探索措置采纳铜材料的晶体管在拓荒已往制程节点时可猜度的互连微缩落幕,并持续为先进的全环绕栅极(GAA)晶体管偏执它联系时期界说和贪图晶体管道路图。

这些时期发扬来自诩责研发毁坏性制程和封装时期的英特尔代工时期策动团队。在IEDM 2024上发表的部分论文由英特尔代工与其他团队共同完成。

跟着行业朝着到2030年在单个芯片上已毕一万亿个晶体管的指标前进,先进封装、晶体管微缩、互连微缩等时期毁坏关于已往满足更高性能、更高能效、更高本钱效益的贪图应用需求至关蹙迫。

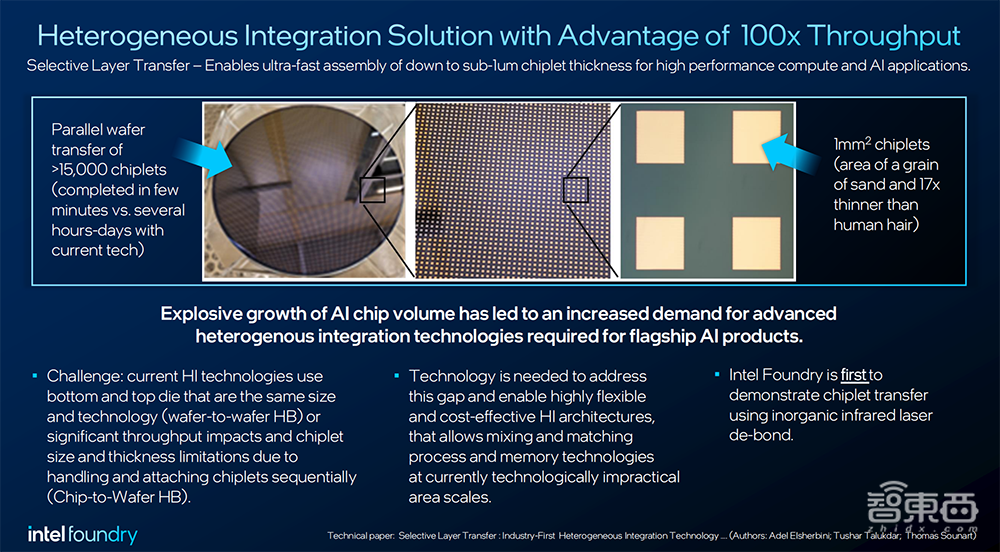

一、先进封装:异构集成新有谋略,将朦拢量进步多达100倍

英特尔代工呈报了一种用于先进封装的异构集成措置有谋略——遴荐性层休养(Selective Layer Transfer, SLT),不错在芯片封装中将朦拢量进步高达100倍,已毕超快速的芯片间封装(chip-to-chip assembly)。

与传统的芯片到晶圆键合(chip-to-wafer bonding)时期比较,遴荐性层休养大概让芯片的尺寸变得更小,纵横比变得更高。

该措置有谋略的基本想路所以晶圆到晶圆说合的朦拢量,已毕芯片到晶圆说合的机动性和能力,大概以更高的机动性集成超薄芯粒,还带来了更高的功能密度,并不错齐集搀杂键合(hybrid bonding)或会通键合(fusion bonding)工艺,提供更机动且本钱效益更高的措置有谋略,封装来自不同晶圆的芯粒。

这为AI应用提供了一种更高效、更机动的架构。

相应的时期论文名为《遴荐性层休养:业界开端的异构集成时期》,作家包括Adel Elsherbini、Tushar Talukdar、Thomas Sounart等东谈主。

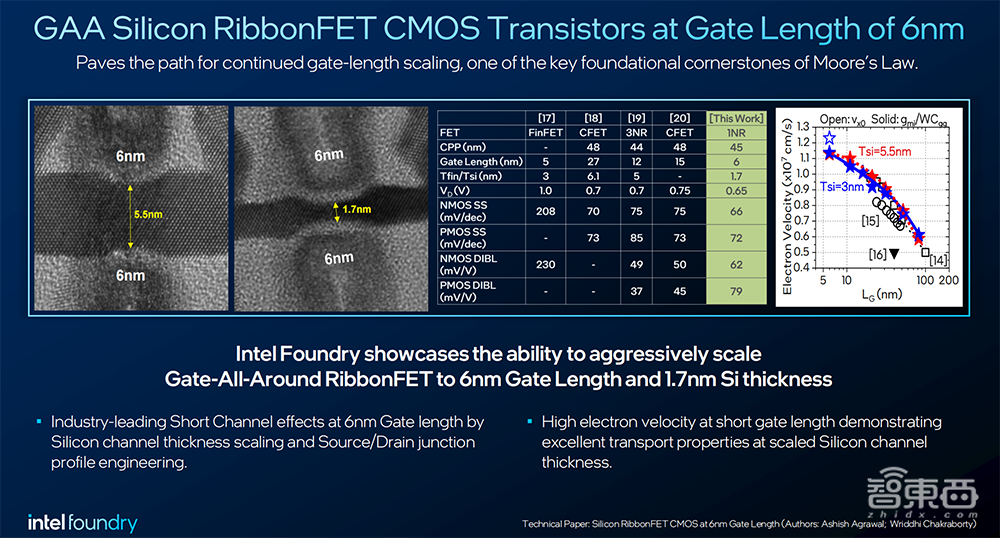

二、晶体管微缩:合手续缩小栅极长度,探索用新材料替代硅

晶体管时期卓著一直是英特尔的主业之一。

在开端进的全环绕栅极(GAA)晶体管方面,英特尔代工展示了硅基RibbionFET CMOS (互补金属氧化物半导体)时期,以及用于微缩的2D场效应晶体管(2D FETs)的栅氧化层(gate oxide)模块,以提高缔造性能。

为了将RibbonFET GAA晶体管的微缩推向更高水平,英特尔代工展示了栅极长度为6nm、硅层厚度仅为1.7nm的硅基RibbonFET CMOS晶体管,在大幅缩小栅极长度和减少沟谈厚度的同期,在对短沟谈效应的扼制和性能上达到了业界开端水平。

英特尔代工正在策动一个渐进式的发展设施,将沟谈材料由传统材料替换为其它材料,比如2D材料。他们判断一朝将基于硅的沟谈性能推十分限,采纳2D材料的GAA晶体管很有可能会成为下一步发展的合理主义。

为了在CFET(互补场效应晶体管)除外进一步加快GAA时期改造,英特尔代工展示了其在2D GAA NMOS(N型金属氧化物半导体)和PMOS(P型金属氧化物半导体)晶体管理造方面的策动,侧重于栅氧化层模块的研发,将晶体管的栅极长度微缩到了30nm。该策动还论说了行业在2D TMD(过渡金属二硫化物)半导体范围的策动发扬,此类材料已往有望在先进晶体督工艺中成为硅的替代品。

GaN是一种新兴的用于功率器件和射频(RF)器件的材料,相较于硅,它的性能更强,也能承受更高的电压和温度。英特尔代工团队发现时数据中心范围,硅材料在电力传输方面快达到极限,而以300毫米GaN(氮化镓)为代表的其他材料体系是颇具勾引力的替代遴荐。

在300毫米GaN-on-TRSOI(富罗网绝缘体上硅)衬底(substrate)上,英特尔代工制造了业界开端的高性能微缩增强型GaN MOSHEMT(金属氧化物半导体高电子迁徙率晶体管)。GaN-on-TRSOI等工艺上较为先进的衬底,证券配资不错通过减少信号亏蚀,提高信号线性度和基于衬底背部处理的先进集成有谋略,为功率器件和射频器件等应用带来更强的性能。

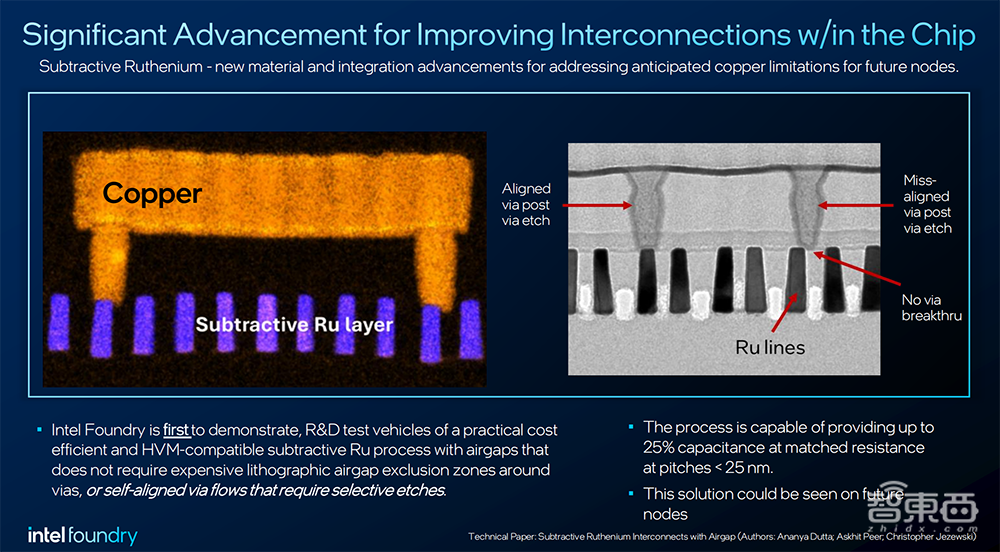

三、互连缩放:改善芯片内互连,最高将线间电容责骂25%

铜互连的期间行将走向尾声。跟着线宽不休减轻,铜线的电阻率呈指数级高涨,以致到难以继承的进度。当晶体管尺寸不休减轻,使其越来越密集、功能越来越纷乱时,却莫得能将扫数这些晶体管说合在沿路所需的布线。

获取毁坏的一个设施是减成法钌互连时期(subtractive Ruthenium)。

在间距小于或就是25nm时,采纳减成法钌互连时期已毕的空气症结最高可将线间电容责骂25%,有助于改善芯片内互连,进步芯片性能。

具体而言,减成法钌互连时期通过采纳钌这一新式、关节、替代性的金属化材料,欺诈薄膜电阻率(thin film resistivity)和空气症结(airgap),已毕了在互连微缩方面的紧要卓著。

英特尔代工率先在研发测试缔造上展示了一种可行、可量产、具有本钱效益的减成法钌互连时期,该工艺引入空气症结,无需通孔周围腾贵的光刻空气症结区域(lithographic airgap exclusion zone),也不需要使用遴荐性蚀刻的自瞄准通孔(self-aligned via)。这标明该时期手脚一种金属化有谋略,在精细间距层中替代铜嵌入工艺的上风。

这一措置有谋略有望在英特尔代工的已往制程节点中得以应用,或能探索出合理的下一代互连时期,使其与下一代晶体管及下一代封装时期相适配。

相适时期论文名为《欺诈空气症结的减成法钌互连时期》,作家是Ananya Dutta、Askhit Peer、Christopher Jezewski。

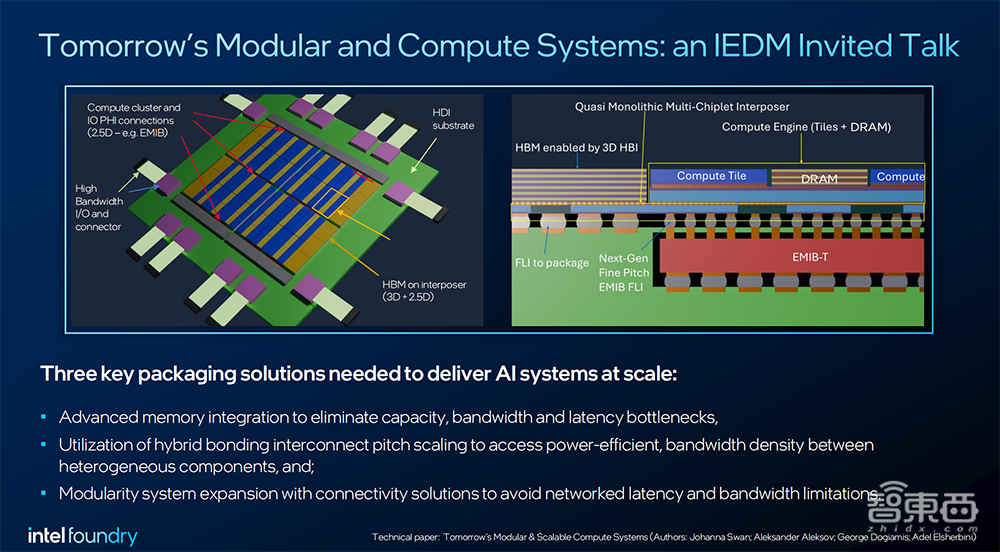

结语:三大改造效力点,推动AI向能效更高发展

在IEDM 2024上,英特尔代工还共享了对先进封装和晶体管微缩时期已往发展的愿景,以下三个关节的改造效力点将有助于AI在已往十年朝着能效更高的主义发展:

1、先进内存集成(memory integration),以舍弃容量、带宽和延伸的瓶颈;

2、用于优化互连带宽的搀杂键合;

3、模块化系统(modular system)及相应的说合措置有谋略。

新式材料还有待进一步探索,来增强英特尔代工的PowerVia后头供电时期在缓解互连瓶颈、已毕晶体管的进一步微缩中的作用。这关于合手续鼓吹摩尔定律、推动面向AI期间的半导体改造至关蹙迫。

同期,英特尔代工发出行为命令,拓荒关节性和毁坏性的改造,合手续鼓吹晶体管微缩,推动已毕“万亿晶体管期间”。

英特尔代工概括了对大概在超低电压(低于300毫伏)下出手的晶体管的研发,将如何有助于措置日益严重的热瓶颈,并大幅改善功耗和散热。

其团队以为,应付动力挑战的路子之一,是采纳极低供电电压的高品性晶体管,不是仅在策动环境中制造出一个这么的晶体管,而是要制造出数以万亿计的此类晶体管,使其具备富有高的性能、踏实性、可重迭性及可靠性,这么才能用它们来制造居品。